# Fine-Grained Compiler Optimization with Split-Schedule-Merge for Specialized Domains

Seungbin Song

The Graduate School

Yonsei University

**Department of Electrical and Electronic Engineering**

## Fine-Grained Compiler Optimization with Split-Schedule-Merge for Specialized Domains

A Dissertation Submitted to the Department of Electrical and Electronic Engineering and the Graduate School of Yonsei University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering

**Seungbin Song**

**June 2024**

# This certifies that the Dissertation of Seungbin Song is approved.

| Thesis Supervisor       | Prof. Hanjun Kim         |

|-------------------------|--------------------------|

| Thesis Committee Member | Prof. Won Woo Ro         |

| Thesis Committee Member | Prof. William Jinho Song |

| Thesis Committee Member | Prof. Youngsok Kim       |

| Thesis Committee Member | Prof. Seonyeong Heo      |

The Graduate School Yonsei University June 2024

## ACKNOWLEDGMENTS

"Surely your goodness and love will follow me all the days of my life, and I will dwell in the house of the LORD forever." - *Psalms 23:6 (NIV)*

항상 선한 길로 인도하시고 인자하심으로 이끌어주신 하나님께 감사드립니다.

학부생의 시작부터 박사 과정의 끝까지 지도해주신 김한준 교수님께 진심으로 감사드립니 다. 10년이 넘는 시간 동안 수많은 조언과 가르침으로 저를 지도하시어 제가 한 명의 연구자로 성장할 수 있도록 해주셨습니다. 교수님께서 주신 가르침을 항상 마음 속에 담고, 앞으로 스스 로의 가치를 증명하고 발전하는 연구자가 될 수 있도록 더욱 정진하겠습니다.

학위 논문 심사를 맡아주신 노원우 교수님, 송진호 교수님, 김영석 교수님, 허선영 교수님 께 감사드립니다. 교수님들께서 주신 값진 피드백과 의견을 반영하여 연구를 더욱 발전시킬 수 있었고, 학술대회 논문을 준비함에 있어 좋은 결과를 얻을 수 있었습니다. 본 연구가 학위 논문 에서 그치는 것이 아니라 향후에 연구를 더 발전시키도록 노력하겠습니다.

저의 박사 과정 동안의 연구는 컴파일러 최적화 연구실의 수많은 선후배들의 도움이 없었 다면 불가능했을 것입니다. 포항에서부터 저를 이끌어주신 선배님이신 이경민 박사님, 김봉준 박사님, 김창수 박사님, 허선영 교수님께 진심으로 감사드립니다. 그리고 연구실에서 동고동락 하며 함께한 이용우 박사, 정신녕, 김동관, 이재호, 최희림, 천선영, 윤성우, 이주민, 권현호, 염호 윤, 이찬, 정건모, 정해은에게 감사드립니다.

저를 낳아주시고 길러주신 사랑하는 부모님께 감사드리고, 박사 학위를 받은 형에게 축하 를 전합니다. 신앙적으로 안식처가 되어준 연세대학교회 대학청년부 목사님과 친구들에게도 감사드립니다. 마지막으로 박사 과정동안 사랑으로 함께한 정민정에게 감사와 사랑을 전합니 다. 이들의 삶 속에 하나님의 사랑과 축복이 가득하길 진심으로 기도합니다.

## **TABLE OF CONTENTS**

| LI                     | LIST OF FIGURES iv |         |                                                            |   |  |

|------------------------|--------------------|---------|------------------------------------------------------------|---|--|

| LI                     | LIST OF TABLES     |         |                                                            |   |  |

| LIST OF ALGORITHMS vii |                    |         |                                                            |   |  |

| ABSTRACT               |                    |         |                                                            |   |  |

| 1.                     | INT                | RODUC   | TION                                                       | 1 |  |

| 2.                     | BAC                | KGROU   | JND & MOTIVATION                                           | 9 |  |

|                        | 2.1                | Netwo   | ork Programming                                            | 9 |  |

|                        |                    | 2.1.1   | Software-Defined Networking                                | 9 |  |

|                        |                    | 2.1.2   | Structure of P4 Language                                   | 1 |  |

|                        |                    | 2.1.3   | Limitations of Existing Network Compilers 1                | 6 |  |

|                        | 2.2                | Tenso   | r Decomposition in Deep Learning                           | 8 |  |

|                        |                    | 2.2.1   | Tensor Decomposition Methods                               | 8 |  |

|                        |                    | 2.2.2   | Number of Operations of Decomposed Convolution Sequences 2 | 1 |  |

|                        |                    | 2.2.3   | Memory Usage of Decomposed Convolution Sequences           | 2 |  |

|                        |                    | 2.2.4   | Limitations of Existing Tensor Decompositions              | 8 |  |

|                        | 2.3                | Motiv   | ation                                                      | 9 |  |

| 3.                     | SPL                | IT, SCH | EDULE, MERGE FOR NETWORK PROGRAMS                          | 2 |  |

|    | 3.1 | Overv   | <i>r</i> iew                                         | 32 |

|----|-----|---------|------------------------------------------------------|----|

|    | 3.2 | Splitti | ing Scheme                                           | 34 |

|    |     | 3.2.1   | Table Decomposition                                  | 34 |

|    |     | 3.2.2   | Dependency Analysis                                  | 36 |

|    | 3.3 | Sched   | luling Scheme                                        | 38 |

|    |     | 3.3.1   | Clock Cycle Estimation                               | 39 |

|    |     | 3.3.2   | Pipeline Scheduling Algorithm                        | 41 |

|    | 3.4 | Mergi   | ing Scheme                                           | 43 |

|    |     | 3.4.1   | Code Generation                                      | 43 |

|    |     | 3.4.2   | Backend Optimization and Function Fusion             | 44 |

| 4. | SPL | IT, SCH | EDULE, MERGE FOR DEEP LEARNING MODELS                | 46 |

|    | 4.1 | Overv   | riew                                                 | 46 |

|    | 4.2 | Splitti | ing Scheme                                           | 48 |

|    |     | 4.2.1   | Tensor Decomposition and Inlining                    | 48 |

|    |     | 4.2.2   | Dependency Analysis                                  | 49 |

|    | 4.3 | Sched   | luling Scheme                                        | 50 |

|    |     | 4.3.1   | Identifying Skip Connections                         | 51 |

|    |     | 4.3.2   | Finding Precedent Reduced Tensors and Restore Layers | 53 |

|    |     | 4.3.3   | Evaluating FLOPS and Memory Trade-Offs               | 56 |

|    |     | 4.3.4   | Replacing Skip Connections                           | 59 |

|    | 4.4 | Mergi   | ing Scheme                                           | 60 |

|    |     | 4.4.1   | Activation Layer Fusion                              | 60 |

|    |     | 4.4.2   | Concatenation Layer Transformation                   | 66 |

| 5. | EVA  | LUATI  | ION                                          | 72   |

|----|------|--------|----------------------------------------------|------|

|    | 5.1  | PSDN   | V Compiler                                   | . 72 |

|    |      | 5.1.1  | Evaluation Setup                             | . 72 |

|    |      | 5.1.2  | Latency                                      | . 74 |

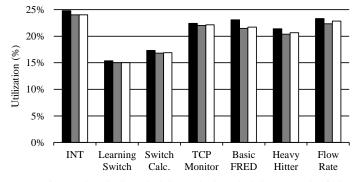

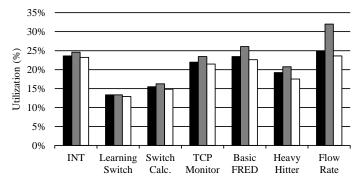

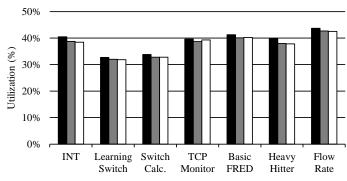

|    |      | 5.1.3  | Resource Utilization                         | . 77 |

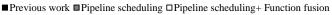

|    |      | 5.1.4  | Throughput                                   | . 80 |

|    | 5.2  | ТеМС   | CO Compiler                                  | . 81 |

|    |      | 5.2.1  | Evaluation Setup                             | . 81 |

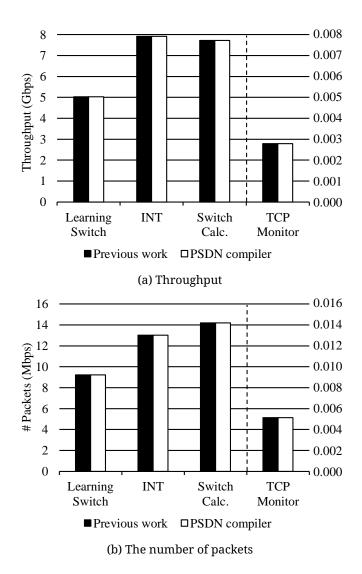

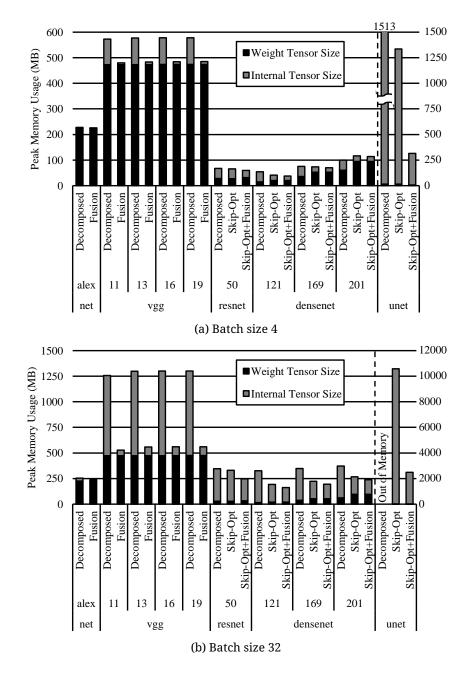

|    |      | 5.2.2  | Peak Memory Usage                            | . 82 |

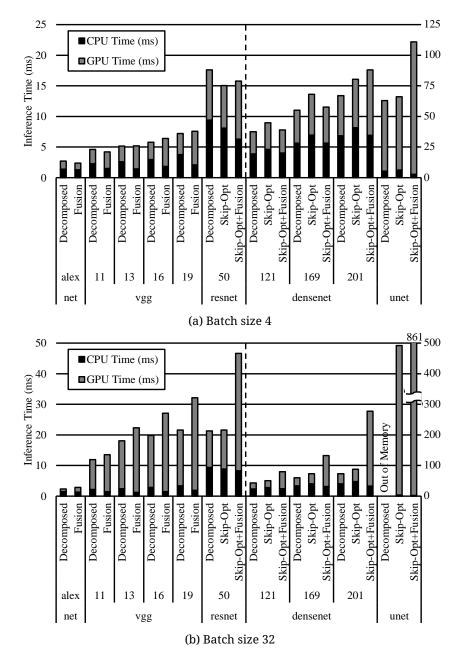

|    |      | 5.2.3  | Inference Time                               | . 84 |

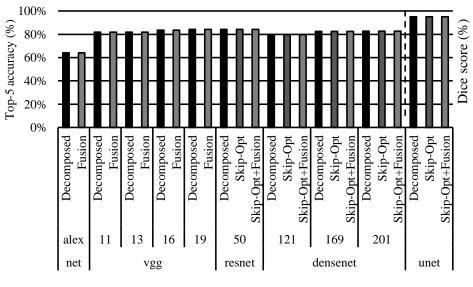

|    |      | 5.2.4  | Accuracy                                     | . 86 |

| 6. | DIS  | CUSSIC | ON                                           | 89   |

|    | 6.1  | PSDN   | V Compiler                                   | . 89 |

|    | 6.2  | ТеМС   | CO Compiler                                  | . 91 |

| 7. | REL  | ATED   | WORK                                         | 95   |

|    | 7.1  | Netw   | vork Compilers                               | . 95 |

|    | 7.2  | Tenso  | or Decomposition                             | . 97 |

|    | 7.3  | DNN    | Framework for Memory-Efficient Deep Learning | . 99 |

| 8. | CON  | ICLUSI | ION                                          | 101  |

| RE | EFER | ENCES  | 3                                            | 103  |

| AI | BSTR | ACT IN | V KOREAN                                     | 127  |

## LIST OF FIGURES

| 2.1 | A brief structure of software-defined networking                                | 10 |

|-----|---------------------------------------------------------------------------------|----|

| 2.2 | The table pipeline's simplified grammar in the P4 language                      | 12 |

| 2.3 | An P4 program example                                                           | 14 |

| 2.4 | The latency percentage of a parser, a table pipeline, and a deparser $\ldots$ . | 15 |

| 2.5 | A P4 table's use (U) and def (D)                                                | 17 |

| 2.6 | Tensor decomposition methods                                                    | 19 |

| 2.7 | Tensor decomposition on a convolution layer                                     | 20 |

| 2.8 | Tensor decomposition on a convolution sequence                                  | 23 |

| 2.9 | Memory usage of internal tensors                                                | 27 |

| 3.1 | The PSDN compiler                                                               | 33 |

| 3.2 | Table decomposition example of Lines 27 to 33 in Figure 2.3                     | 34 |

| 3.3 | Match and action functions of Table forward in Figure 2.3                       | 35 |

| 3.4 | Code motion on match functions                                                  | 36 |

| 3.5 | Program dependence graph                                                        | 37 |

| 3.6 | Function cycle estimation                                                       | 39 |

| 3.7 | A scheduled pipeline                                                            | 43 |

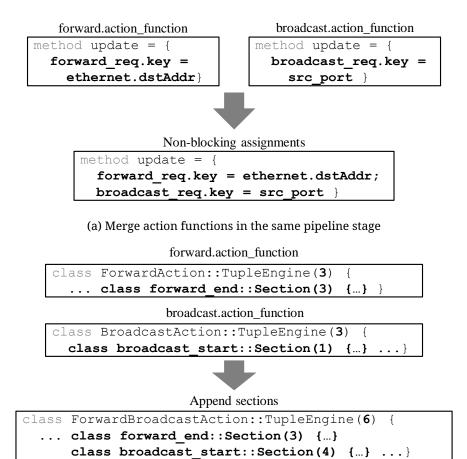

| 3.8 | Function fusion methods                                                         | 45 |

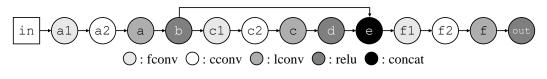

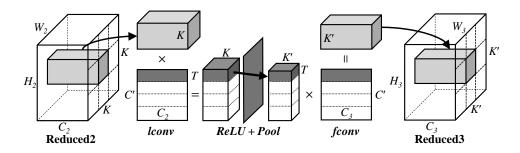

| A fused pipeline                                                   | 45                 |

|--------------------------------------------------------------------|--------------------|

| The TeMCO compiler                                                 | 47                 |

| Tensor decomposition example                                       | 48                 |

| Program dependence graph                                           | 49                 |

| Skip connection optimization example                               | 53                 |

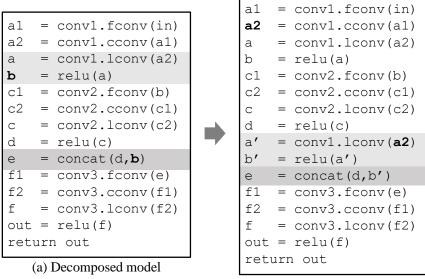

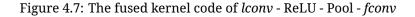

| Fused layer in Figure 2.8c                                         | 60                 |

| The fused kernel code of <i>lconv</i> - ReLU - <i>fconv</i>        | 62                 |

| The fused kernel code of <i>lconv</i> - ReLU - Pool - <i>fconv</i> | 63                 |

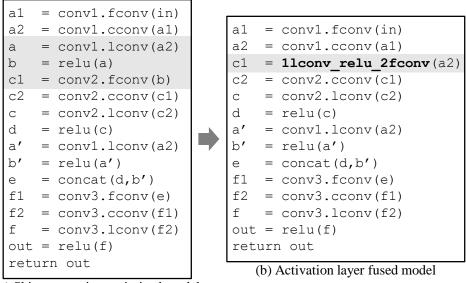

| Activation layer fusion code example                               | 65                 |

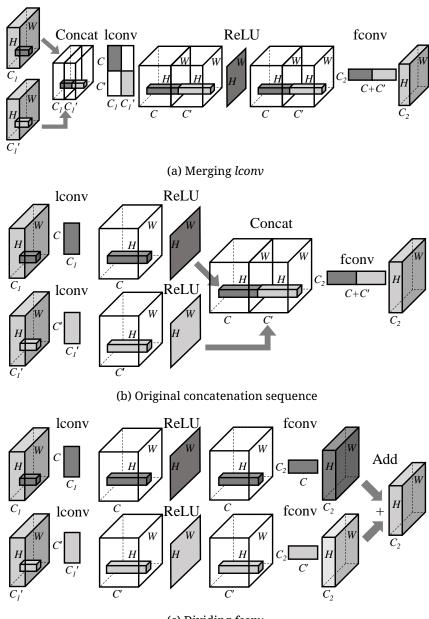

| Concatenation layer transformation                                 | 67                 |

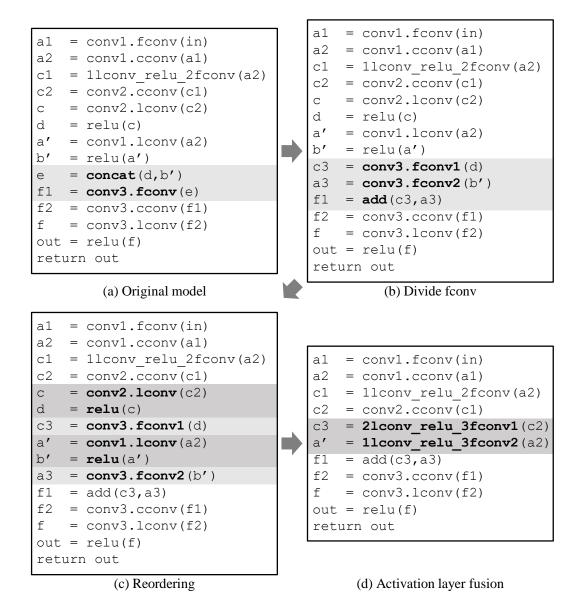

| Dividing <i>fconv</i> code example                                 | 69                 |

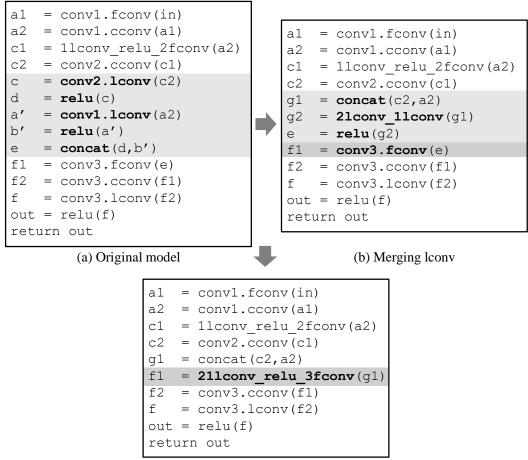

| Merging <i>lconv</i> code example                                  | 70                 |

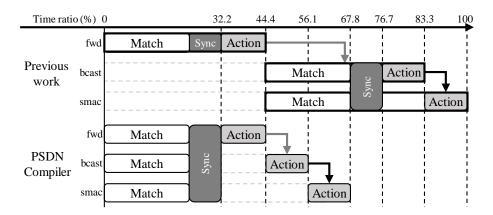

| Packet processing latency                                          | 74                 |

| Latency of functions in Learning Switch                            | 75                 |

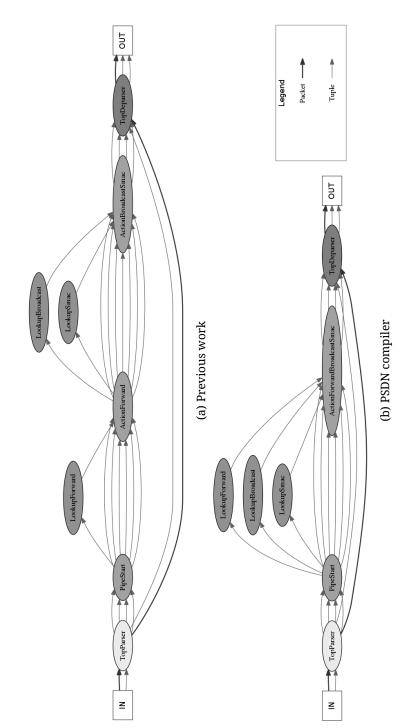

| PDG of Learning Switch translated into SDNet IR                    | 76                 |

| Resource utilization                                               | 78                 |

| Throughput and the number of processed packets                     | 79                 |

| Peak memory usage                                                  | 83                 |

| End-to-end inference time                                          | 85                 |

| Accuracy                                                           | 86                 |

|                                                                    | The TeMCO compiler |

## LIST OF TABLES

| 3.1 | Cycle estimation of match functions       | 40 |

|-----|-------------------------------------------|----|

| 5.1 | P4 benchmarks from P4-NetFPGA GitHub [76] | 73 |

| 5.2 | Accuracy with ADMM training [15, 17]      | 87 |

## LIST OF ALGORITHMS

| 3.1 | Pipeline scheduling algorithm              | 42 |

|-----|--------------------------------------------|----|

| 4.1 | Skip connection optimization               | 50 |

| 4.2 | Liveness analysis                          | 52 |

| 4.3 | Finding reduced tensors and restore layers | 54 |

| 4.4 | Computation and memory overhead check      | 56 |

## ABSTRACT

## Fine-Grained Compiler Optimization with Split-Schedule-Merge for Specialized Domains

Domain-specific languages support programmabilities for programmers to implement and extend functions that fulfill the users' demands. Defining operations and interfaces of functions with some granularity allows programmers to compose domainspecific programs with the functions easily. Although the encapsulated functions entirely express the programs' functionalities, existing compilers do not fully optimize the programs because of the coarse granularity.

In software-defined Networking (SDN), existing compilers miss opportunities to parallelize fine-grained functions. They treat each packet processing table, which includes both match and action functions, as a single task unit. Therefore, they parallelize the programs without breaking down the match and action functions and analyzing dependencies between them.

In the domain of deep learning inference, existing compilers do not fully optimize fine-grained convolutions of tensor-decomposed deep learning models. They apply tensor decomposition on convolution weights and generate decomposed convolution sequences. However, because they only replace convolutions with the corresponding decomposed convolution sequences, they do not reorder or fuse the decomposed convolutions in a whole model perspective and lose opportunities to minimize memory usage. This research proposes novel fine-grained compilers using a split-schedule-merge scheme for network programming and deep learning inference. It presents a new compiler named PSDN for network programming, which splits packet processing tables into match and action functions, schedules them into a pipeline, and merges the functions to reduce synchronization overheads. Additionally, for deep learning inference, it introduces a new compiler called TeMCO that splits decomposed convolution sequences into separated convolution layers, schedules the execution order of restore layers, and merges the decomposed convolution layers with non-decomposed layers. Through the split-scheme-merge scheme, the compiler can find more fine-grained parallelism opportunities in SDN programs and reduce peak memory usage in tensor-decomposed deep learning models.

The compilers of this work enhance the performance of domain-specific programs with the split-schedule-merge schemes. Compared to previous approaches, the PSDN compiler achieves a 12.1% reduction in packet processing time and a 3.5% decrease in resource utilization of seven network programs. The TeMCO compiler reduces peak memory usage of internal tensors by 75.7% with 1.08× to 1.70× inference time overheads of 10 decomposed models of five deep learning architectures. The compilers of this work can achieve performance gains on their domain-specific programs by utilizing the split-schedule-merge schemes tailored to their specific domains.

Keywords: Compilers, Networks, Deep Learning

## **1. Introduction**

The demand for high-performance computing in server environments using domainspecific accelerators is ever-increasing. As applications become more complex and data volumes grow exponentially, traditional CPU-based server architectures struggle to keep pace with the required processing speeds. To address these challenges, server-side acceleration technologies such as smart network interface cards (SmartNICs) and graphic processing units (GPUs) have emerged as powerful solutions. SmartNICs offload and accelerate network processing tasks, freeing CPU resources and enhancing overall system efficiency, particularly in network function virtualization (NFV). As another example, GPUs, with their parallel processing capabilities, are well-suited for compute-intensive tasks, providing significant performance boosts for workloads such as machine learning, data analytics, and scientific computing.

Coupled with these hardware advancements, the rise of domain-specific languages (DSLs) offers tailored support for specific application domains, facilitating more efficient and expressive programming models. DSLs enable developers to write concise code that directly utilizes specialized accelerators like SmartNICs and GPUs. This synergy between server-side acceleration technologies and DSLs allows for optimized performance and simplified development workflows, driving innovations across various fields, from high-frequency trading to deep-learning acceleration. By harnessing the power of SmartNICs and GPUs with DSL support, modern server architectures can meet the demands of applications, pushing the boundaries of what is achievable in computing performance and efficiency.

One of the key points that DSLs can provide efficient and expressive programmability for GPUs and SmartNICs is *abstraction*. That is, DSLs support programmers to implement their specialized functionalities by granulating them into functions. In the domain of Software-Defined Networking (SDN), recent network programming languages enable programmers to create a program that is composed of multiple functional units called *packet processing tables*. In the field of deep learning inference, tensor decomposition provides methods that decompose a convolution layer into the corresponding *decomposed convolution sequence*, regarding the sequence as the representative functional unit of the convolution layer.

Recent advancements in network programming languages enable programmers to construct network services on programmable network switches equipped with multiple subdivided functional units. The OpenFlow specification [1] initially outlined a programmable switch architecture that utilizes these multiple units. Subsequently, the P4 programming language [2] introduced a programming model based on these divisions. Each unit is represented by a *packet processing table* that includes *match* and *action* functions. The *match* function evaluates packet header values against the rules in the control plane, while the *action* function modifies internal metadata or packet header values based on the results of this comparison. For instance, programmers can use these tables to implement features like access control lists (ACLs) [3], Ethernet switching (layer-2) [4], IP routing (layer-3) [5], and equal-cost multi-path (ECMP) routing [6]. Network service providers then integrate these tables into a control flow and deploy the configured network service on various platforms such as CPUs [7, 8, 9], FPGAs [10], or specialized packet processors [11, 12, 13].

In deep learning inference, tensor decomposition schemes decompose a convolution weight into factorized weights and generate a *decomposed convolution sequence* to substitute for the original convolution layer. Tensor decomposition [14, 15, 16, 17, 18, 19] is one of model compression schemes such as pruning [20, 21, 22, 23, 24, 25], quantization [26, 27, 28, 29, 30, 31], and knowledge distilation [32, 33, 34, 35, 36]. Tensor decomposition lowers computational complexity by applying mathematical methods to break down a convolution into a series of smaller convolutions. This technique involves factorizing a large-weight tensor from an original convolution into multiple smaller-weight tensors. As a result, the *decomposed convolution sequence* of factorized weight tensors generates an output tensor that closely approximates the output of the original convolution using the initial weight tensor. Therefore, existing research using tensor decomposition substitutes the convolution layers in the original model with decomposed convolution sequences, and they become functional units that represent the original convolutions.

Even though encapsulated functions express functionalities of domain-specific programs, existing compilers do not fully optimize the programs due to their coarse granularity. The existing network compilers [37, 38, 39] regard each packet processing table as a task unit and parallelize programs while match and action functions are aggregated. On the other hand, the existing tensor decomposition methods [14, 15, 16, 17, 18, 19] encapsulate decomposed convolutions into a sequence and do not reorder or fuse the convolutions individually, so they lose opportunities to minimize memory usage by using internal tensors within the encapsulated decomposed convolutions.

A P4 program consists of match and action functions that read and modify various packet header values, allowing some parts of these functions to be executed concurrently. However, existing compilers [37, 38, 39] treat each packet processing table as a single task unit and schedule the execution order of the tables while keeping match and action functions intact. These compilers manage data dependencies between tables in a coarse-grained manner and assign all the tables to the physical pipeline of packet processors. As a result, they miss opportunities for fine-grained parallelism between match and action functions. To fully exploit these opportunities for parallelism, a network compiler should split packet processing tables into individual match and action functions and strategically schedule these match and action functions, rather than the whole tables, into the pipeline.

In decomposed convolution sequences in tensor-decomposed deep learning models, tensors within the decomposed convolution sequences have reduced sizes and memory usage. However, the existing tensor decomposition methods [14, 15, 16, 17, 18, 19] do not decapsulate the decomposed convolution sequences and lose opportunities to minimize memory usage of whole model inference by using the reduced tensors. These methods replace convolution layers with the corresponding decomposed convolution sequences. Inside the sequences, the channel sizes of tensors are reduced with decomposed convolutions, but they soon recover to their original sizes. This is because following non-decomposed layers, such as pooling or activations, require the tensors with the original sizes as their inputs, and skip connections store the tensors with the original sizes for the latter layers. Therefore, these methods do not reduce the memory usage of whole model inference. To minimize the peak memory usage of tensor-decomposed models, a deep-learning compiler should utilize the reduced tensors not only in the decomposed convolution sequences but also through the model by replacing the original tensors with the reduced tensors.

To overcome the coarse granularity of the existing domain-specific compilers, this work proposes fine-grained compilers using split-schedule-merge schemes that optimize network programs and decomposed deep learning models. A splitting scheme decomposes the coarse-grained abstracted functional units into fine-grained functions, analyzing data and control dependencies among them. A scheduling scheme calculates and estimates computation and memory overheads of the decomposed functions and schedules the execution order of the functions while preserving the dependencies. Finally, a merging scheme fuses the functions to minimize synchronization overheads and function calls. These methods are augmented in the network compiler called PSDN and the tensor-decomposed deep learning compiler called TeMCO.

This work introduces PSDN, a novel compiler that reorganizes the network function programs with fine-grained functional units written in the P4 language to reduce packet processing latency. The PSDN compiler follows split, schedule, and merge schemes to parallelize network programs with subdivided functional units. First, the compiler splits packet processing tables into decomposed match and action functions and analyzes the control and data dependencies between them. The compiler generates a program dependence graph (PDG) for the split functions. Next, the compiler estimates the processing latency for each function based on their execution behavior and strategically schedules these functions within a packet processing pipeline, considering both PDG and estimated latencies. To minimize the pipeline's length, the compiler assigns independent functions wherever possible to the same pipeline stage. In the final phase, to reduce synchronization overheads among the functions, the compiler merges concurrently running functions within the same stage, as well as serially executed functions in the pipeline. The compiler generates a program in PX language [40], which is suitable for synthesis into FPGA-based network switches [10].

This work also proposes TeMCO, compiler optimizations for minimizing tensors' memory usage across tensor decompositions of deep learning inference. The TeMCO compiler replaces the usage of original internal tensors with reduced tensors by utilizing a split-schedule-merge scheme. First, the compiler splits a decomposed convolution sequence into the first, core, and last convolution layers and considers them individual optimizable units. Second, the compiler schedules the execution order of restore layers required in skip connections and duplicates the layers at the end of these connections to substitute original internal tensors with reduced tensors. Finally, the compiler merges non-decomposed activation layers with decomposed convolution layers. These fused layers avoid allocating input and output internal tensors and instead operate solely with the reduced tensors. As a result, these compiler transformations enable the continuous and unimpeded use of reduced tensors throughout the inference process, eliminating the need for tensor restoration.

The compilers of this work utilize split-schedule-merge schemes to improve the performance of domain-specific programs. The compilers split abstracted functional units of the domain-specific programs into fine-grained functions, exposing optimization opportunities for parallelization and memory usage reduction. Then, the compilers schedule the execution orders of fine-grained functions, maintaining the original dependencies and semantics of the programs. Finally, the compilers merge the functional units with subsequent ones to reduce computation costs and memory overheads. The splitschedule-merge scheme is shared in the PSDN compiler and the TeMCO compiler, improving the packet processing latency of network programs and the peak memory usage of tensor-decomposed deep learning models, respectively.

This work evaluates the PSDN compiler prototype with seven P4 programs [41] and synthesizes these programs onto the NetFPGA-SUME board [10]. The evaluation experiment analyzes the end-to-end packet processing latency through HDL simulation and measures the resource consumption of arithmetic logic units (ALUs), registers, and memories by synthesizing the compiled program into the SmartNIC. In comparison to prior work [39], the PSDN compiler achieves a 12.1% reduction in packet processing latency and a 3.5% decrease in resource utilization.

This work evaluates the TeMCO compiler prototype using 10 models from five deep learning architectures, including image classification with deep learning models [42, 43, 44, 45], as well as image segmentation with UNet [46]. The evaluation experiment benchmarks these against baseline models decomposed using the Tucker decomposition [47], with TeMCO's optimizations applied. The evaluation results demonstrate that TeMCO reduces the peak memory usage of internal tensors by 75.7% while adding an inference time overhead of between 1.08× and 1.70× across various batch sizes. Importantly, the optimizations implemented by TeMCO do not compromise the accuracy of the decomposed models. Contributions of this work are:

- fine-grained compiler optimizations that decapsulate functional units and reorganize domain-specific programs with split-schedule-merge schemes,

- a new fine-grained network compiler named PSDN that converts a P4 networking program into a PX program for Xilinx SDNet,

- a splitting scheme for a network program that decouples match and action functions of packet processing tables,

- a scheduling scheme for a network program that schedules the decoupled functions into a pipeline with dependency analysis and clock cycle estimation,

- a merging scheme for a network program that combines the functions in the concurrent and subsequent stages to decrease both latency and resource usage,

- TeMCO's compiler optimizations that replace the uses of original tensors with reduced tensors and reduce peak memory usage in decomposed model's inferences,

- a splitting scheme for a decomposed deep learning (DL) program that considers decomposed convolution layers as individual layers,

- a scheduling scheme for a decomposed DL program that schedules the execution orders of restore layers in skip connections,

- and a merging scheme for a decomposed DL program that fuses the decomposed convolution layers with non-decomposed activation layers.

## 2. Background & Motivation

This section provides background on network programming and tensor decomposition in deep learning inference. In the domain of network programming, it describes the concept of software-defined networking (SDN) and introduces the structure of data plane language. In the field of deep learning inference, it describes tensor decomposition and the memory usage of tensor-decomposed models. Finally, it investigates the limitations of existing network compilers and tensor decomposition compilers.

#### 2.1 Network Programming

#### 2.1.1 Software-Defined Networking

Software-defined networking (SDN) decouples the control plane from the data plane in network switches, enabling them to be both controllable and programmable. Open-Flow [1] provides APIs to facilitate communication between the control and data planes, while ONOS [48] offers a control platform.

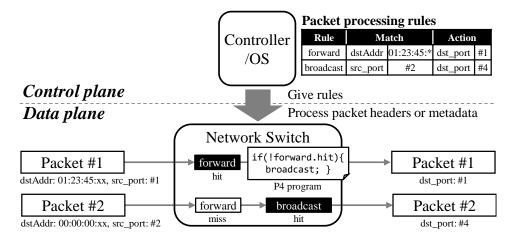

Figure 2.1 illustrates the packet processing structure of SDN. In the control plane, network service providers define *packet processing rules* for how network switches process packets based on their headers or metadata. In Figure 2.1, the Controller/OS provides packet processing rules: forward and broadcast. First, the rule forward checks

Figure 2.1: A brief structure of software-defined networking

whether the packer header value dstAddr starts with 01:23:45 and modifies the metadata dst\_port to #1. Second, the rule broadcast checks whether the packet header value src\_port is #2 and modifies the metadata dst\_port to #4.

In the data plane, a network switch processes packets according to these predefined rules. In Figure 2.1, the network switch is programmed with a program written in the P4 language [2]. The rule forward and broadcast are applied to the corresponding *packet processing tables*. The example P4 program describes that if the table forward misses, apply the table broadcast. In the first case, the programmed network switch processes Packet #1, whose dstAddr starts with 01:23:45. Because the match of the table forward hits, the switch modifies the metadata dst\_port to #1 and passes the table broadcast. In the second case, the switch processes Packet #2, whose dstAddr starts with 00:00:00 and src\_port is #2. Because the match of the table forward misses, the switch applies the table broadcast and modifies the metadata dst\_port to #4 as src\_port is #2 and the table broadcast matches.

The development of data plane languages and reconfigurable network switch architectures has made the data plane programmable. Network service providers can now program switches to support newly defined protocols or execute multiple network functions across different protocols using data plane languages rather than relying solely on built-in functions. One popular data plane language is P4 [2]. For instance, in-band Network Telemetry (INT) [49], load balancing [50] and in-network computation [51] have all been implemented using the P4 language. In Figure 2.1, the network switch can be programmed with the P4 program to conduct designated network packet processing.

#### 2.1.2 Structure of P4 Language

P4 [2] is a domain-specific language designed for packet processing. While this work focuses on the P4 language, other languages, such as Huawei's Protocol-Oblivious Forwarding [52, 53], share a similar structure. A data plane program in these languages comprises three main components: a parser, a table pipeline, and a deparser. The parser accepts packets and generates packet headers and metadata according to network protocols. Using the parsed headers and metadata, the table pipeline modifies them with tables applying rules defined in the control plane. Finally, the deparser packages all the information and emits the modified packets.

Figure 2.2 illustrates a segment of the simplified P4 grammar related to the table pipeline. To simplify the example, this paper omits the definitions of headers, metadata, the parser, and the deparser. The table pipeline includes action functions, table declarations, an apply function, and extern functions. The extern functions are implemented outside of the program, such as Verilog modules. Because the P4 program does

| table_pipeline := control table_pipeline_name() {            | args := arg, args            |

|--------------------------------------------------------------|------------------------------|

| action_decl_list                                             | := arg                       |

| table_decl_list                                              | arg := type id               |

| extern_decl_list                                             | key_list := key_list; key    |

| <pre>apply { stmt_list; } }</pre>                            | := key                       |

| action_decl_list := action_decl_list action_decl             | key := id : match_type       |

| := action_decl                                               | match_type := exact          |

| action_decl := action action_name(args) {    stmt_list;    } | := lpm                       |

| table_decl_list := table_decl_list table_decl                | := ternary                   |

| := table_decl                                                | id := packet header          |

| table_decl := table table_name {                             | or metadata field            |

| key = { key_list; }                                          | expr_list := expr_list, expr |

| actions = { action_name_list; }                              | := expr                      |

| <pre>default_action = action_name; }</pre>                   | expr := <i>bool</i>          |

| action_name_list := action_name_list;                        | := <i>int</i>                |

| := action_name                                               | := id                        |

| extern_decl := extern extern_name(args);                     | := (expr)                    |

| stmt_list := stmt_list; stmt                                 | := lop expr                  |

| := stmt                                                      | := expr op expr              |

| stmt := id = expr                                            | := table_name\               |

| := if(expr) {stmt_list;}                                     | .apply().hit                 |

| := if(expr) {stmt_list;} else {stmt_list;}                   |                              |

| := table_name.apply()                                        |                              |

| := action_name(expr_list)                                    |                              |

| := extern_name(expr_list)                                    |                              |

|                                                              |                              |

Figure 2.2: The table pipeline's simplified grammar in the P4 language

not describe the implementation details of the extern functions, these functions are considered as a black box. On the other hand, the action functions are composed of various statements such as assignments, if conditions, and function calls. These functions modify packet header values or metadata or call other functions or tables.

The table declaration consists of a list of *keys* and *actions* defined within the table pipeline. These keys include the IDs of match variables, such as packet headers or metadata, and the types of matches. The types of matches include exact, 1pm, and ternary. The exact match checks whether the values are the same, the 1pm finds the longest prefix matches, and the ternary match finds the most similar match, including *don't care* term. The tables can be called using a app1y method, and app1y().hit returns the result of the table matches. The table compares the keys with rules from the control plane and conducts the designated action of the matched rule.

Figure 2.3 illustrates an example P4 pseudo program in Figure 2.1. The table pipeline in the example includes action definitions, tables, and an apply function. An *action* definition is a function that modifies packet headers (hdr) or metadata (meta). Some actions, such as set\_output\_port and set\_broadcast, require arguments. These argument values are in packet processing rules provided by the control plane. Additionally, actions can modify packet headers or metadata either directly or by using external functions. A *table* definition includes *keys* consisting of packet headers or metadata for matches and *actions* that invoke actions when the keys are matched. The *apply* function serves as the main function, outlining the control flow. It can include conditional branches like if statements, but the P4 language does not support loops or iterations. Therefore, the P4 program results in an acyclic control flow for the table pipeline.

```

1 parser Parser(packet_in packet, out headers hdr,

inout metadata meta) {...}

2

3

4 control TablePipeline(inout headers hdr, inout metadata meta) {

action set_output_port(port_t port) {

5

6

meta.dst_port = port;

7

}

8

table forward {

key = { hdr.ethernet.dstAddr: lpm; }

9

actions = {

10

11

set_output_port;

12

NoAction;

}

13

default_action = NoAction;

14

15

}

action set_broadcast(port_t port) {

16

meta.dst_port = port;

17

18

}

19

table broadcast {

20

key = { meta.src_port: exact; }

actions = {

21

22

set_broadcast;

23

NoAction;

24

}

default_action = NoAction;

25

}

26

27

apply {

28

// forward based on destination Ethernet address

if (!forward.apply().hit) {

29

30

// miss, then broadcast

broadcast.apply();

31

32

}

}

33

34 }

35

36 control Deparser(packet_out packet, in headers hdr) {...}

37

38 Switch(Parser(), TablePipeline(), Deparser()) main;

```

Figure 2.3: An P4 program example

Figure 2.4: The latency percentage of a parser, a table pipeline, and a deparser

In the P4 program shown in Figure 2.3, the table forward uses the Ethernet destination address (hdr.ethernet.dstAddr) with the lpm match option as a key (Line 9) and includes two actions: set\_output\_port and NoAction (Lines 10 to 13). When the control plane provides a rule with the Ethernet destination address (01:23:45:xx), the network switch compares this address with the destination address of incoming packets. If the addresses match, the switch sets the destination port number (meta.dst\_port) to the value #1 specified by the control plane using the set\_output\_port action. If the addresses do not match, the table forward passes the packet by default action NoAction. In this case, the table broadcast is applied, as defined in the apply function (Lines 27 to 33). The table broadcast compares the source port number meta.src\_port with the rule and modifies meta.dst\_port to #4 if the value exactly matches.

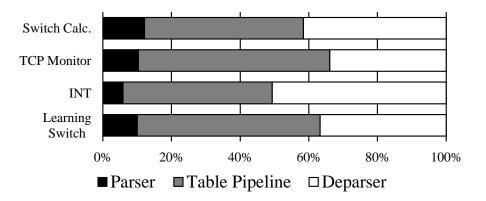

Although a data plane program includes a parser, a table pipeline, and a deparser, this work concentrates on optimizing the table pipeline, as it consumes the majority of the execution time in the data plane. Figure 2.4 shows the latency percentage of four P4 programs in HDL simulations. The latency of table pipelines takes 49.4% of overall latency in geomean. The parser extracts packets with predefined protocols, and the deparser packages the packets with the processed data. Compared to the parser and the deparser, the table pipeline incurs overheads due to its reading and writing of packet header fields and metadata. Moreover, previous research [54] shows that the latency of the table pipeline increases sharply as the number of tables grows. Therefore, this work aims to optimize the table pipeline to reduce the packet processing latency in programmable switches.

## 2.1.3 Limitations of Existing Network Compilers

Although P4 [2] supports programmability and flexibility of network switches, current P4 compilers [11, 37, 38, 39] do not fully optimize network programs due to the lack of fine-grained dependency analysis. The existing compilers [11, 38] detect data dependencies in the case that a table modifies a packet header or metadata field and the following table uses this field in a match (match dependency) or alters it in an action (action dependency). However, these approaches only focus on table-level data dependencies, resulting in coarse-grained pipeline scheduling that misses potential parallelism opportunities among match and action operations.

Table-level dependency analysis treats a packet processing table as an atomic unit, overlooking the finer details of matches and actions. Figure 2.5 illustrates the definition of *use* and *def* within a table. Although match keys and actions have their own uses and defs, existing compilers analyze these only at the table level to identify data dependencies. To fully utilize parallelism opportunities at a finer granularity, it is necessary to decouple matches and actions from the tables in data dependency analysis.

U(key) := { id } D(key) := Ø  $U(key_{list}) := U(key_{list}) \cup U(key)$ := U(key)  $D(key_{list}) := D(key_{list}) \cup D(key)$ := D(key)  $U(stmt) := \{ id \mid id \in expr \}$  $:= \{ id \mid id \in expr \} \cup U(stmt\_list)$  $D(stmt) := \{ id \}$ := D(stmt\_list)  $U(stmt_list) := U(stmt_list) \cup (U(stmt) \setminus D(stmt_list))$  $D(stmt_list) := D(stmt_list) \cup D(stmt)$ U(action\_decl) := U(stmt\_list) D(action decl) := D(stmt list) U(action\_name) := U(action\_decl | action\_decl.action\_name = action\_name) D(action\_name) := D(action\_decl | action\_decl.action\_name = action\_name) U(action\_name\_list) := U(action\_name\_list) ∪ U(action\_name) D(action\_name\_list) := D(action\_name\_list) ∪ D(action\_name)  $U(table_decl) := U(key_list) \cup U(action_name_list)$ D(table\_decl) := D(action\_name\_list)

Figure 2.5: A P4 table's use (U) and def (D)

While decomposing tables into match functions and action functions can uncover additional parallelism opportunities, it may also lead to increased computation and area overheads in the synthesized hardware. Existing compilers [37, 39] allocate tables to hardware pipeline stages, synthesizing control flows at the table level. Combining match and action functions within a single module can reduce synchronization overheads because the compiler does not have to place synchronization barriers for every function but for tables. However, a fine-grained compiler scheme that separates match and action functions into different pipeline stages may result in an increased number of stages and more complex control flows. This complexity can lead to unnecessary synchronization, potentially increasing the overall execution time despite shorter individual pipeline stages. Therefore, it is essential for a P4 compiler to simplify the control flows by pipeline scheduling and to reduce the number of pipeline stages by merging functions.

## 2.2 Tensor Decomposition in Deep Learning

#### 2.2.1 Tensor Decomposition Methods

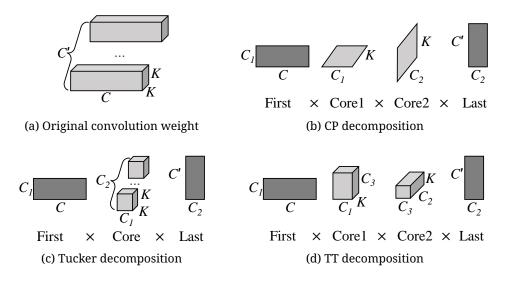

Tensor decomposition methods decompose weight tensors into core weights and lowranked factor matrices. Tensor decomposition types include Canonical Polyadic Decomposition (CP) [55], Tucker Decomposition [15, 47], and Tensor Train Decomposition (TT) [17, 56]. Figure 2.6 depicts how different tensor decompositions break down a convolution weight tensor into smaller tensors. There are two 2D factor matrices: *first* and *last*. The width and the height of the first factor matrix are the channel size of the input (C) and reduced channel ( $C_1$ ), and the width and the height of the last factor matrix are reduced channel ( $C_2$ ) and the channel size of the output (C'). The *core weights* have lower dimensions or reduced channels than the original weight tensor. The shape of the core weights is different depending on the tensor decomposition methods, but the methods in Figure 2.6 all have the first and the last 2D factor matrices. The following figures in this paper will use a core weight of Tucker decomposition (Figure 2.6c) as a base example for simplicity, but the core weights can be replaced depending on the de-

Figure 2.6: Tensor decomposition methods

composition types. Multiplication of the core weights and the 2D factor matrices is an approximation of the original weight tensor.

In tensor decomposition, selecting appropriate *ranks* influences the quality of the decomposition and its effectiveness in compressing tensors. In Figure 2.6, the channel sizes  $C_1$  to  $C_3$  represent ranks of the decomposition. The ranks of the core weights and the factor matrices determine the level of approximation achieved and the amount of compression attained. Generally, higher ranks result in better approximation accuracy but require more computational and spatial resources. Conversely, lower ranks may lead to more significant compression but at the expense of increased approximation accuracy.

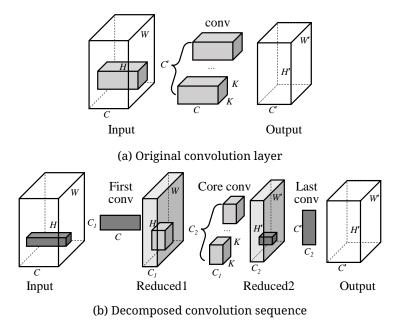

With the factor matrices and the core tensor, tensor decomposition can construct a *decomposed convolution sequence* that approximates the computation of a convolution

Figure 2.7: Tensor decomposition on a convolution layer

layer. Figure 2.7 describes an original convolution layer and the corresponding decomposed convolution sequence. In the two factor matrices in Figure 2.6, the First matrix and the Last matrix become weights of  $1 \times 1$  convolution layers named First conv and Last conv in Figure 2.7b, respectively. The core convolution layer(s) (Core conv in Figure 2.7b) has the decomposed core weight(s) (Core in Figure 2.6). Note that while the core convolutions vary across different types of tensor decomposition, the first and final convolution layers remain consistent among these methods.

The first convolution layer reduces an input channel size (C) to a reduced channel size ( $C_1$ ). The core convolution layer performs a reduced-sized convolution, accepting the reduced input channel size ( $C_1$ ) and generating a reduced output channel size ( $C_2$ ). Finally, the last convolution layer restores the reduced channel size ( $C_2$ ) to an output channel size (C'). In the rest of the paper, this work will refer to the first convolution layer as *fconv*, the last convolution layer as *lconv*, and the internal tensors within a decomposed convolution sequence (Reduced1 and Reduced2 in Figure 2.7b), of which the channel sizes are reduced, as *reduced tensors*.

## 2.2.2 Number of Operations of Decomposed Convolution Sequences

This work measures the reduction of the number of operations achieved through tensor decomposition. By decomposing tensors, tensor decomposition effectively reduces the computational complexity of convolution operations, primarily by reducing the channel size of the core convolution layer. The original convolution layer in Figure 2.7a requires the number of multiplication operations described in Equation (2.1).

$$CC'K^2H'W' \tag{2.1}$$

In Equation (2.1),  $K^2$  represents the size of the convolution kernel, C denotes the number of input channels, and C', H', and W' represent the number of output channels, height, and width of the output tensor, respectively. The height and width of the output tensor (H' and W') are calculated based on the input dimensions (H and W) and the size of the convolution kernel (K), where H' = H - K + 1 and W' = W - K + 1.

The decomposed convolution sequence in Figure 2.7b requires the number of multiplication operations described in Equation (2.2).

$$CC_1HW + C_1C_2K^2H'W' + C_2C'H'W'$$

(2.2)

In Equation (2.2), C represents the number of input channels,  $C_1$ ,  $C_2$ , and C' denote the number of channels after each decomposition step, and H and W represent the height and width of the input tensor, respectively. The dimensions H' and W' of the output tensor are calculated similarly to the original convolution layer, where H' = H - K + 1 and W' = W - K + 1. Comparing Equation (2.1) with Equation (2.2), the decomposed convolution sequence involves fewer multiplication operations due to the reduction in the number of input and output channels after each decomposition step. Assuming that the Tucker decomposition reduces channel sizes with decomposition ratio r, the reduced channel sizes  $C_1$  and  $C_2$  follow these equations:  $C_1 = rC$  and  $C_2 = rC'$ . Then, Equation (2.2) can be rewritten as follows in Equation (2.3):

$$rC^{2}HW + r^{2}CC'K^{2}H'W' + rC'^{2}H'W'$$

(2.3)

This example shows that tensor decomposition can reduce the number of operations. Previous work [15] proposes a tensor decomposition scheme that finds decomposition ratios (i.e., ranks) of convolution layers to reduce FLOPS and inference time of a model. However, the scheme fails to reduce memory usage of the model inference. The following section describes the memory usage analysis of tensor-decomposed models and why the previous scheme fails to reduce the memory usage.

## 2.2.3 Memory Usage of Decomposed Convolution Sequences

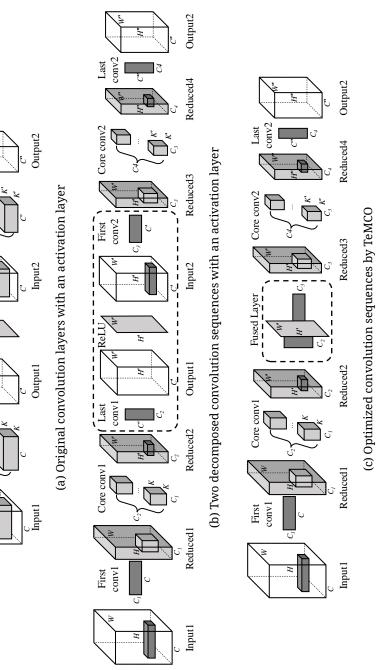

This work analyzes the peak memory usage of models decomposed by tensor decomposition. To inspect peak memory usage, we analyze a sequence of two consecutive

conv2

ReLU

convl

23

convolution layers and one activation layer between them rather than a single convolution layer. In Figure 2.8, we observe two convolution layers and one activation layer between them, as well as two sequences of decomposed convolutions with an activation layer. The peak memory usage of a model is determined by the memory requirements of two key types of tensors: *weight tensors* (parameters, filters, and kernels) and *internal tensors* (input and output tensors of layers, also known as feature maps). When measuring the peak memory usage influenced by internal tensors, it is essential to include activation layers like ReLU followed by convolution layers for an accurate assessment of peak memory usage.

In the context of model inference, deep learning frameworks, such as PyTorch [57] and TensorFlow [58], adopt a strategy of loading complete weight tensors before executing the inference. This approach involves initializing and storing all the weight tensors associated with the model's convolution layers. In Figure 2.8a, the size of the weight tensors for the convolution layers is outlined by Equation (2.4):

$$CC'K^2 + C'C''K'^2 \tag{2.4}$$

In Figure 2.8b, the size of the weight tensors in the decomposed convolution sequences is described by Equation (2.5):

$$CC_1 + C_1C_2K^2 + C_2C' + C'C_3 + C_3C_4K^2 + C_4C''$$

(2.5)

If the tensor decomposition reduces channel sizes with decomposition ratio r, the reduced channel sizes  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  of reduced tensors follow these equations:  $C_1 = rC$ ,  $C_2 = C_3 = rC'$  and  $C_4 = rC''$ . Then, Equation (2.5) can be rewritten as follows in Equation (2.6):

$$rC^{2} + r^{2}CC'K^{2} + 2rC'^{2} + r^{2}C'C''K^{2} + rC''^{2}$$

(2.6)

While tensor decomposition effectively reduces the memory usage of weight tensors, it does not directly impact the memory usage of internal tensors allocated by deep learning frameworks. These frameworks manage memory allocation and deallocation for internal tensors dynamically. This dynamic memory management strategy involves allocating memory only for the internal tensors required by the currently active layer during model inference. Additionally, memory allocated to tensors that are no longer needed for subsequent inference tasks is promptly released.

In Figure 2.8, this work analyzes the peak memory usage of internal tensors by computing the maximum size of input and output tensors for each layer. This approach provides insights into the memory requirements imposed by the internal tensors within the model architecture. For the case of the two convolution layers illustrated in Figure 2.8a, the peak memory usage related to internal tensors is quantified using Equation (2.7):

$$MAX(CHW + C'H'W', 2C'H'W', C'H'W' + C''H''W'')$$

(2.7)

Assuming that  $H \approx H'$ ,  $W \approx W'$  and  $C \approx C' \approx C''$ , Equation (2.7) is reduced as follows in Equation (2.8):

$$2CHW$$

(2.8)

Similar to calculating the peak memory usage of the internal tensors in the convolution sequences associated with an activation layer, this work calculates the peak memory usage of the internal tensors in Figure 2.8b as follows in Equation (2.9):

$$\begin{aligned} MAX (CHW + C_1HW, C_1HW + C_2H'W', \\ C_2H'W' + C'H'W', 2C'H'W', C'H'W' + C_3H'W', \\ C_3H'W' + C_4H''W'', C_4H''W'' + C''H''W'') \end{aligned} \tag{2.9}$$

The channel sizes of the reduced tensors (denoted as  $C_1$  to  $C_4$ ) are smaller compared to those of the internal tensors (denoted as C to C''). This is because tensor decomposition reduces the channel sizes of convolution kernels. Then, this work simplifies Equation (2.9) as follows in Equation (2.10):

$$2C'H'W'$$

(2.10)

Here, the resulting size calculated from Equation (2.10) closely resembles the approximate size calculated using Equation (2.8). The memory usage of the internal tensors within the activation layer has a significant influence on the overall peak memory usage of the decomposed convolution sequences. Therefore, it is necessary to hide the allocation of internal tensors within the activation layer to reduce peak memory usage.

This analysis highlights that while tensor decomposition reduces the memory usage of weight tensors, it does not directly reduce the peak memory usage associated with internal tensors. The dominance of internal tensor memory usage within the activation

Figure 2.9: Memory usage of internal tensors

layers underscores the challenge of further reducing peak memory usage solely through decomposition methods. Consequently, achieving comprehensive memory reduction in tensor-decomposed models requires complementary strategies beyond tensor decomposition. The following section examines the actual memory usage of decomposed deep learning models and discusses the limitations of previous work.

## 2.2.4 Limitations of Existing Tensor Decompositions

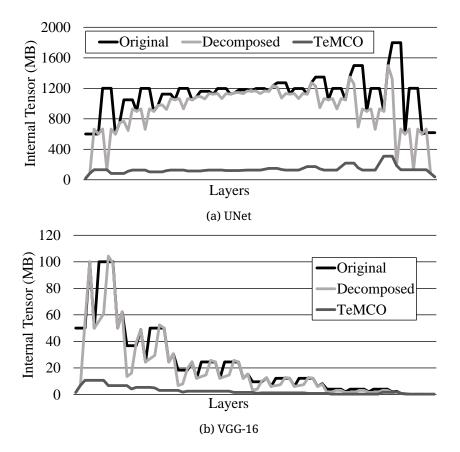

The existing tensor decomposition schemes [14, 15, 16, 17, 18] miss the opportunity to further reduce peak memory usage of internal tensors despite tensor decomposition using less memory for decomposed convolution sequences. To illustrate the impact of skip connections and activation layers, this work compares the memory usage of internal tensors in the original and decomposed models using Tucker decomposition [47]. Figure 2.9 show the memory usage of internal tensors during 4-batch inference with UNet [46] and VGG-16 [43] on RTX 4090.

In Figure 2.9a, skip connections account for 76.2% of the peak memory usage by internal tensors in the tensor-decomposed model of UNet. The UNet architecture features an hourglass shape with skip connections horizontally linking the downsampling and upsampling blocks. During decomposed model inference, the downsampling blocks' decomposed convolution sequences restore reduced tensors to their original sizes, while the original tensors remain in the skip connections until the upsampling blocks use them. As a result, memory usage by skip connections in the decomposed model is comparable to that of the original model.

Conversely, in Figure 2.9b, the peak memory usage by internal tensors occurs during the computation of non-decomposed activation layers in VGG-16. VGG has a linear sequence of convolution, activation, and pooling layers. In the decomposed model of VGG-16, decomposed convolution sequences reduce the internal tensor sizes during core convolutions. However, these sequences soon restore the reduced tensors to their original sizes to be processed in non-decomposed activation layers. Thus, the peak memory usage caused by non-decomposed layers in the decomposed model is similar to that in the original model.

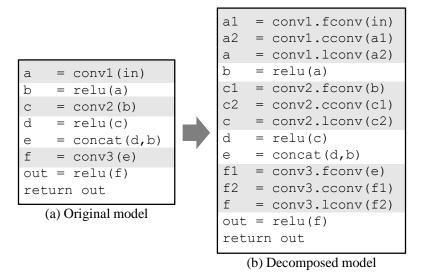

To address this issue, a new compiler optimization is needed to decapsulate the decomposed convolution sequences and to transform the decomposed deep-learning model to use only reduced tensors, as shown in Figure 2.8c. Figure 2.8c displays the optimized convolution sequence comprising reduced tensors, achieved by fusing *lconv1*, ReLU and *fconv2*, and removing Output1 and Input2 from Figure 2.8b. Since Figure 2.8b did not include the skip connections, the compiler optimization schemes require more sophisticated steps to handle complex data flows with decapsulated convolutions.

## 2.3 Motivation

To overcome the limitations of existing domain-specific compilers for network programming and tensor decomposition, this work proposes compilers that operate in finer granularity. These compilers decapsulate coarse-grained functional units into finer-grained functions, analyze their data and control dependencies, optimize programs by scheduling the functions, and fuse the functions to minimize synchronization overheads. This *split-schedule-merge* concept is shared in both the proposed network programming compiler and tensor decomposition compiler, decomposing coarse-grained functional units into finer-grained functions, scheduling the functions preserving dependencies, and merging the functions to reduce computation and memory overheads.

This work proposes PSDN, a compiler utilizing the split-schedule-merge scheme for network function programs written in P4. To overcome the limitations of existing compilers that optimize programs at the table level, PSDN splits packet processing tables into *matches* and *actions* and schedules and merges the split functions of the programs. The PSDN compiler consists of table decomposition and dependency analysis as a splitting scheme, cycle estimation and pipeline scheduling as a scheduling scheme, and function fusion and code generation as a merging scheme.

The PSDN compiler decouples match and action functions and analyzes the control and data dependencies among them. It then estimates the processing latency of each function based on their execution behaviors and allocates the functions efficiently in a pipeline while respecting these dependencies and latency estimations. To minimize pipeline length, the compiler places independent functions into the same pipeline stage. Finally, the PSDN compiler generates a program written in the PX language [40], which can be synthesized into FPGA-based network switches [10]. To simplify the resulting hardware and reduce synchronization overheads, the compiler also fuses concurrent functions within the same pipeline stage and consecutive functions in the pipeline. With these optimizations, the PSDN compiler reduces the latency of packet processing by 12.1% and utilization of LUTs, registers, and memory by 3.5% in geomean.

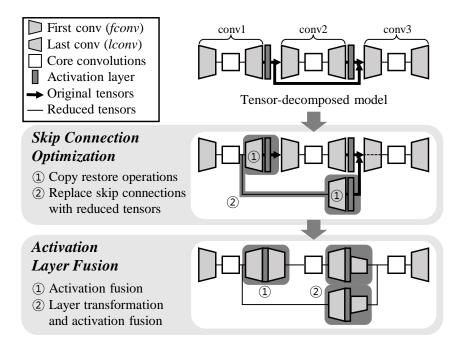

This work also proposes the TeMCO compiler that utilizes the split-schedule-merge scheme for the deep learning models with tensor decomposition applied. TeMCO splits *fconv* and *lconv* from decomposed convolution sequences, schedules the execution orders of restore layers in skip connections and copies them, and merges *lconv* and *fconv* with non-decomposed activation layers in the decomposed models. The TeMCO compiler consists of inlining as a splitting scheme, skip connection optimization as a scheduling scheme, and activation layer fusion and concatenation layer transformation as a merging scheme.

The TeMCO compiler inlines the decomposed convolution layers and analyzes the dependencies of the layers in a model. It then finds skip connections, identifies reduced tensors of skip connections, copies required layers that restore the original tensors of the skip connections, inserts the copied layers into the end of skip connections, and replaces the original tensors with the reduced tensors. To avoid allocation of the original tensors in non-decomposed activation layers, the TeMCO compiler fuses the activation layer with *lconv* and *fconv*, which are alongside the activation layer. Finally, TeMCO transforms concatenation layers that are placed at the end of skip connections to apply activation layer fusion fully. With these optimizations, TeMCO reduces the memory usage of internal tensors by 75.7% of tensor-decomposed models, with 1.08× to 1.70× overheads of inference time in 4 to 32 batch sizes. Furthermore, the compiler optimizations of TeMCO do not reduce the accuracy of the decomposed models.

# 3. Split, Schedule, Merge for Network Programs

This chapter presents an overview of a split-schedule-merge scheme of the PSDN compiler for network programs. The compiler 1) splits match and action functions in packet processing tables, analyzing data and control dependencies and generates a program dependency graph, 2) schedules execution orders of functions into the pipeline regarding the dependencies and estimated clock cycles, and 3) merges concurrent and subsequent action functions and finally generates a PX program which is synthesizable to FPGA-based SmartNICs. The PSDN compiler reduces latency and resource utilization of network function programs with these optimizations.

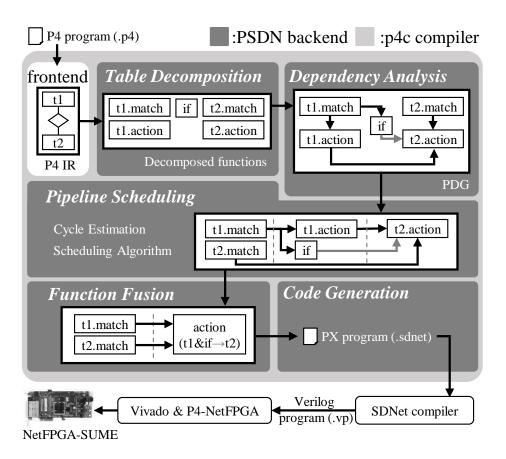

#### 3.1 Overview

Figure 3.1 provides an overview of the PSDN compiler. The frontend of the PSDN compiler is the p4c open-source compiler [59], which generates P4 intermediate representation (IR). Based on the P4 IR, the PSDN compiler decomposes P4 tables into match functions and action functions (Section 3.2.1). It then analyzes data and control dependencies among the functions and combines them into a program dependence graph (PDG), with prefetching of read-only functions (Section 3.2.2). After generating the PDG, the compiler performs cycle estimation and schedules the order of the function executions into a pipeline (Section 3.3). To minimize pipeline length, it allocates independent func-

Figure 3.1: The PSDN compiler

tions to the same pipeline stage. Finally, the compiler performs function fusion, merging adjacent action functions (Section 3.4).

The role of this compiler is to translate a P4 IR to a PX program and optimize it. Other parts of the compilation process utilize the p4c compiler as the frontend and the SD-Net compiler [60] as the backend. The PSDN compiler is implemented on top of the p4c compiler, with backend passes developed to translate P4 IR to an optimized PX program. Once the PSDN compiler generates the optimized PX program, the SDNet compiler trans-

Figure 3.2: Table decomposition example of Lines 27 to 33 in Figure 2.3

lates it into a protected (encrypted) Verilog program, concealing the implementations of translated modules. Since the SDNet compiler hides the details of the translated modules, RTL (register transfer-level) optimizations are impossible. Currently, this work follows the workflow of P4-NetFPGA-SUME [41], which includes the SDNet compiler. Still, future work aims to develop an end-to-end compiler for high-level synthesis and to overcome pipeline limitations. The Verilog programs are synthesized using Vivado 2018.2 and tested on the NetFPGA-SUME board [10]. The evaluation infrastructure is detailed in Section 5.1.

# 3.2 Splitting Scheme

#### 3.2.1 Table Decomposition

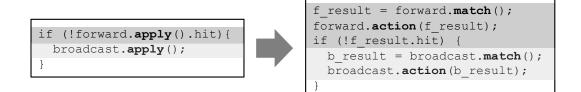

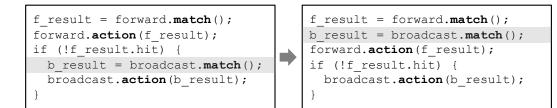

The PSDN compiler employs a table decomposition scheme that splits match functions and action functions for P4 tables. Figure 3.2 illustrates the decomposition of the table pipeline (Lines 27 to 33) from Figure 2.3. Initially, the PSDN compiler decomposes forward.apply() into forward.match() and forward.action(). The transformed code calls forward.match() and stores the return value in f\_result. The forward.action() function then performs actions using f\_result as an argument.

```

1 typedef enum { exact, lpm, ternary } LookupType;

2 typedef struct { bool hit; int action_id;

int* args; } Result;

3

4

5 Result ForwardTable::match(LookupType type, int* keys) {

Result result = PERFORM_MATCH(type, keys);

6

return result;

7

8 }

9

10 void ForwardTable::action(Result result) {

if(result.hit) {

11

switch(result.action_id){

12

//case 1: set_output_port(), default: NoAction()

13

case 1: meta.dst_port = result.args[0]; break;

14

default: break;

15

16

}

}

17

18 }

```

Figure 3.3: Match and action functions of Table forward in Figure 2.3

The if statement requires the hit-or-miss result of the table forward as the condition is !f\_result.hit. The table decomposition also decomposes the table broadcast into broadcast.match() and broadcast.action().

The table decomposition decouples match and action functions into separated instruction blocks. Figure 3.3 lists the decoupled match and action functions of the table forward from Figure 2.3. For simplicity, this work uses C++ semantics to describe the match and action functions. The match function handles the key match operation of the P4 table, receiving key variables as input, comparing with packet processing rules in the control plane, and returning a hit-or-miss result, a selected action number, and arguments. The action function determines whether to execute the actions based on the match result and performs the specified action with the given arguments. Note that the table decomposition inlines each action function into the switch cases of

Figure 3.4: Code motion on match functions

ForwardTable::action (Line 14 in Figure 3.3). By applying the table decomposition, these match and action functions become separated instruction blocks.

P4 semantics allow direct instructions in the table pipeline, meaning the P4 apply block can contain conditional branches (e.g., Line 29 in Figure 2.3) or assignment statements. To simplify dependency analysis, the PSDN compiler translates these instructions into separate instruction blocks. Finally, the table decomposition generates instruction blocks with matches, actions, and condition instructions.

## 3.2.2 Dependency Analysis

The PSDN compiler's dependency analysis follows traditional data and control dependency analysis methods [61, 62]. It identifies data dependencies using the *use* and *def* information illustrated in Figure 2.5. The compiler constructs a program dependence graph (PDG) by combining data and control dependencies. Before constructing the PDG, the compiler redirects control dependencies from the table to the action function to prefetch read-only match functions.

The PSDN compiler conducts *code motion* on read-only functions and prefetches them. Match functions and certain extern functions are *stateless*, meaning that they

Figure 3.5: Program dependence graph

neither modify the program's state nor depend on the control flow. Figure 3.4 demonstrates how the PSDN compiler handles stateless functions. The match function only compares keys with control plane rules, reading variables without changing the program's state. Similarly, some extern functions like register-read and hash operate in the same way. The PSDN compiler moves condition-invariant function calls outside the conditional branches for stateless functions, thereby combining the control dependency with the action function. The prefetching enhances parallelization opportunities, as seen with the match functions of forward and broadcast in Figure 3.4 and reduces the execution time after the if statement.

Figure 3.5 presents the PDG for the example code in Figure 2.3. The match and action functions can have data dependencies. The forward and broadcast action functions

have a data dependency because they modify the same metadata field. The if statement requires f\_result.hit to determine the execution of the broadcast match function. Since the broadcast match function is stateless and not data-dependent on the if statement, the PSDN compiler draws the control dependency from the if statement to the broadcast action function.

In terms of data dependence, the compiler can resolve *false* dependencies through variable renaming with a static single assignment (SSA) form. However, this work opts not to resolve false dependencies. Variable renaming requires additional instructions, which can introduce overhead on resource utilization and latency. For instance, the forward and broadcast action functions have write-after-write dependencies. A compiler could allocate these functions in parallel by renaming meta.dst\_port another name, but this would require additional resources on registers to save the local results. Furthermore, the metadata field meta.dst\_port is a global variable, meaning that the local modification in both forward and broadcast should be synchronized. Therefore, this work decides not to resolve these dependencies to avoid additional resource usage and synchronization overheads.

## 3.3 Scheduling Scheme

The PSDN compiler schedules the execution order of functions in the PDG and maps them into a pipeline. To reduce the pipeline length, the pipeline scheduler allocates independent functions within the same pipeline stage. It begins by estimating the latencies in clock cycles of each function and then uses a greedy-based algorithm to allocate the functions efficiently.

Figure 3.6: Function cycle estimation

# 3.3.1 Clock Cycle Estimation

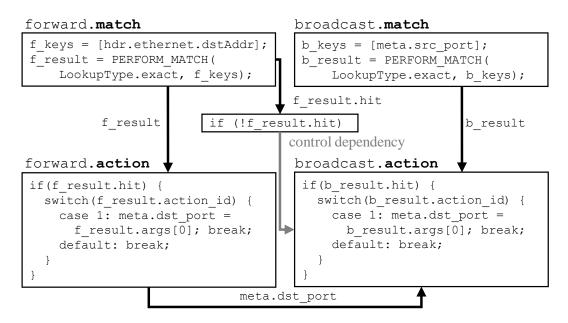

Figure 3.6 shows clock cycle estimation of the PSDN compiler. The PSDN compiler estimates the required clock cycles for each function block. This paper describes the estimation methods of match, action, and extern functions.

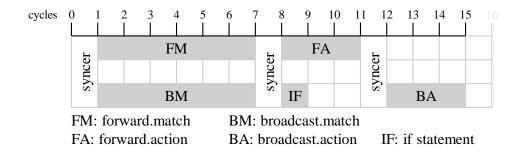

The cycles for match functions depend on their types: exact match, ternary match, and lpm match. Although the cycle estimation formulas for match functions depend on their specific implementations, this work abstracts the execution models of these functions with the number of entries (depth, d) and length of a key (width, w). Table 3.1

Table 3.1: Cycle estimation of match functions

| Lookup type | Estimated cycles                                                             |

|-------------|------------------------------------------------------------------------------|

| exact       | 6                                                                            |

| lpm         | $20 \ (= 2\log(256) + 4)$                                                    |

| ternary     | 20 (= $2\log(256) + 4$ )<br>2 $\lfloor \log(\lceil w/40 \rceil) \rfloor + 6$ |

shows the cycle estimation of the match functions used by the PSDN compiler, setting d = 256 and referenced from Xilinx documentation [63, 64, 65].

An exact match function (Figure 3.6a) uses a content-addressable memory (CAM) that conducts a parallel search to find an exact match of entries with a key. Therefore, the exact match function takes a constant latency.

An 1pm match function (Figure 3.6b) finds the longest prefix match (LPM) to search keys. Calculating the length of the prefix match of each entry is constant, but finding the longest length takes more time when the number of entries (depth) is large. This process requires multiplexers to compare each entry with a binary search. Therefore, the estimated latency of the 1pm match function is a linear function of log(d).

A ternary match function (Figure 3.6c) uses a ternary-CAM (TCAM) module that accepts don't-care terms (X) as elements of entries. The TCAM module finds the most similar match of entries with a key. Thus, TCAM requires multiplexers for width and depth dimensions to calculate the similar match for each entry and find the most similar match. The estimated cycles are a linear function of log(w) and log(d).

For action functions (Figure 3.6d), non-blocking assignments that are independent of each other take one cycle. Each blocking assignment and conditional statement also takes one cycle. For conditional branches, the estimator sums up the cycles of the longest branch. Therefore, the estimated latency of the action functions equals the number of instructions in the longest branch minus the number of non-blocking assignments.

For extern functions (Figure 3.6e), the PSDN compiler treats them as a *black box*. Since the compiler does not know how a programmer implements the extern function, the programmer should provide information about the maximum latency of the extern function through an annotation (@maxLatency). Then, the PSDN compiler parses this annotation to determine the estimated cycles of the extern function.

The backend FPGA hardware uses different clock rates for action functions and match/extern functions. The clock period for match and extern functions is twice as long as for instructions in action functions. This difference in clocks is also considered when estimating the cycles. Therefore, the estimated clock cycles of the extern function (Figure 3.6e) are twice as long as the annotated cycles, and the estimated clock cycles of the match functions (Table 3.1) are multiple of two.

## 3.3.2 Pipeline Scheduling Algorithm

With a PDG and estimated cycles of functions, the pipeline scheduler allocates the functions to a pipeline. Algorithm 3.1 illustrates the pipeline scheduling of the PSDN compiler. The algorithm first identifies the functions that do not have any dependencies (I)from the PDG and identifies the next-independent functions (N) whose dependencies are resolved once the functions in I are allocated. Next, the algorithm identifies the functions (R) that are required to resolve the dependencies of the functions in N.

The algorithm allocates all functions in R within the pipeline stage and determines where to allocate the functions in  $I \setminus R$ . Where to allocate the function  $v \in I \setminus R$  in a

Algorithm 3.1: Pipeline scheduling algorithm

```

Input : A program dependence graph G = (v, e)

Output : A scheduled pipeline P that is a list of pipeline stages

// PRED(v): predecessors of v

// SUCC(v): successors of v

1 P \leftarrow \emptyset

<sup>2</sup> while G \neq \emptyset do

I \leftarrow \{v \mid v \in G \text{ s.t. } \mathsf{PRED}(v) = \emptyset\}

3

N \leftarrow \bigcup_{v \in I} \mathsf{SUCC}(v)

4

R \leftarrow \bigcup_{v \in N} \mathsf{PRED}(v)

5

V \leftarrow \text{Sort } v \in I \setminus R in assending order of \text{Latency}(v)

6

for v \in V do

7

if Latency(v) \leq MaxLatency(R) then

8

R \leftarrow R \cup \{v\}

9

else if MaxLatency(R) > MaxLatency(N) then

10

R \leftarrow R \cup \{v\}

11

end

12

end

13

// ⊕: concatenation operator

P \leftarrow P \oplus R

14

G \leftarrow G \setminus R

15

16 end

```

pipeline stage depends on Latency (v) over MaxLatency (R) and MaxLatency (N). The scheduling algorithm selects either the current stage (R) or the next stage (N) whose MaxLatency is larger than Latency (v). If Latency (v) is larger than MaxLatency (R) and MaxLatency (N), the scheduler opts for the stage with the longer MaxLatency. These steps are repeated until all functions in the PDG (G) are allocated.

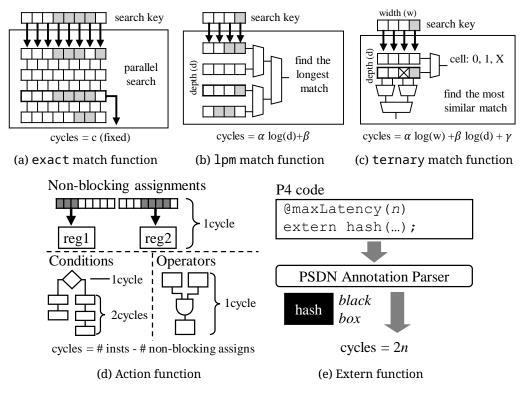

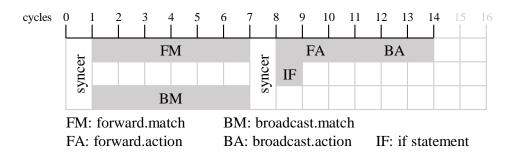

Figure 3.7 illustrates an example of pipeline allocation for the PDG shown in Figure 3.5. The pipeline scheduling algorithm allocates functions that are independent of each other to the same pipeline stage. In Figure 3.7, forward and broadcast match

Figure 3.7: A scheduled pipeline

functions are located in the same stage. Functions allocated to the same pipeline stage are executed in parallel.

To synchronize data of each pipeline stage, the PSDN compiler inserts a synchronization barrier called a *syncer* between stages. A syncer receives results from the preceding stage, updates metadata and global packet header values, and transmits them to the next stage. Because the syncer introduces additional clock cycles, inserting too many syncers would increase latencies and diminish parallelization benefits. Consequently, the PSDN compiler employs a function fusion scheme to minimize the number of syncers, as discussed in the following section.

# 3.4 Merging Scheme

## 3.4.1 Code Generation

The code generation of the PSDN compiler follows a similar approach to the P4-SDNet compiler [39]. The PSDN compiler translates instructions in action functions and basic blocks into PX instructions within tuple engines. A tuple engine in the PX language [40] consists of multiple *sections* that contain assignment statements (*update*) and a jump operation to the next section (*move\_to\_section*). The PSDN compiler groups non-blocking assignment statements into the same section and translates conditional statements into the *move\_to\_section* operation.

#### 3.4.2 Backend Optimization and Function Fusion